# ELT256.120.90 Transparent Display

# ELT256.120.90

# **Operation Manual**

#### **Table of contents:**

| 1 | ELT2                        | 256.1   | 20.90 transparent TFEL display    | . 4 |  |

|---|-----------------------------|---------|-----------------------------------|-----|--|

|   | 1.1                         | Feat    | ures and benefits                 | . 4 |  |

| 2 | 2 Installation and handling |         |                                   | . 4 |  |

|   | 2.1                         | Mour    | nting TFEL display                | . 4 |  |

|   | 2.2                         | Cable   | e length                          | . 5 |  |

|   | 2.3                         | Clear   | ning                              | . 5 |  |

|   | 2.4                         | Avoid   | ding latent image                 | . 5 |  |

| 3 | Spec                        | cificat | ions                              | . 5 |  |

|   | 3.1                         | Cont    | rol basics                        | . 5 |  |

|   | 3.2                         | Powe    | er                                | . 5 |  |

|   | 3.3                         | Conr    | nectors                           | . 6 |  |

|   | 3.3.                        | 1       | Output connector J2, high voltage | . 6 |  |

|   | 3.3.2                       | 2       | Output Connector J4, logic        | . 7 |  |

|   | 3.3.3                       | 3       | Input connector J1                | . 8 |  |

|   | 3.3.4                       | 4       | Input connector J1 descriptions   | . 8 |  |

|   | 3.4                         | Displ   | lay video input timing            | . 9 |  |

|   | 3.4.                        | 1       | VCLK polarity selection           | . 9 |  |

|   | 3.4.2                       | 2       | Internal frame buffer             | . 9 |  |

|   | 3.4.3                       | 3       | Video timing limits               | 10  |  |

|   | 3.5                         | Envir   | ronmental specification           | 11  |  |

|   | 3.5.                        | 1       | Temperature                       | 11  |  |

|   | 3.5.2                       | 2       | Humidity                          | 11  |  |

|   | 3.6                         | Elect   | romagnetic Compatibility          | 12  |  |

|   | 3.7                         | RoHS    | 5                                 | 12  |  |

|   | 3.8                         | Relia   | bility                            | 12  |  |

|   | 3.9                         | Mech    | nanical Specifications            | 12  |  |

|   | 3.9.                        | 1       | Controller board                  | 12  |  |

|   | 3.9.2                       | 2       | Driver module                     | 12  |  |

|   | 3.9.3                       | 3       | Panel active area                 | 12  |  |

|   | 3.9.                        | 4       | Pixel pitch                       | 12  |  |

|   | 3.9.                        | 5       | Pixel size                        | 13  |  |

|   | 3.9.                        | 6       | Fill factor                       | 13  |  |

|   | 3.9.                        | 7       | Component envelope                | 13  |  |

|   | 3.9.8                       | 8       | Mechanical drawings               | 13  |  |

|   | 3.10                        | Optio   | cal specifications                | 16  |  |

|   | 3.10                        | .1      | "ON" luminance                    | 16  |  |

|   | 3.10                        | .2      | Maximum "OFF" luminance           |     |  |

|   | 3.10                        | .3      | Luminance non-uniformity          |     |  |

|   | 3.10                        | .4      | Chromaticity                      | 16  |  |

| 4 | Desc                        | criptio | on of warranty                    | 17  |  |

| 5 | Ordering information 18     |         |                                   |     |  |

Date: June 19, 2017

Olarinluoma 9 FI-02200 Espoo Finland

Tel. +358 9 7599 530 Fax +358 9 7599 5310 lumineq@beneq.com

# **Operation Manual** ELT256.120.90 Display

| 6 | Support and service | 18   |

|---|---------------------|------|

| 7 | RoHS II             | . 18 |

Date: June 19, 2017

# 1 ELT256.120.90 transparent TFEL display

The ELT256.120.90 display from Lumineq® Displays is a 256 column by 120 row TASEL® transparent electroluminescent display utilizing thin film electroluminescent (TFEL) technology.

The ELT256.120.90 consists of two parts. One part is a controller board. The second part is a display module which consists of a driver board, two connector boards, the TFEL glass panel, and two heat seals all encased in a plastic frame. The product includes the cables which connect the display module to the controller board.

#### 1.1 Features and benefits

- Excellent visual performance

- Wide viewing angle ~360°, fully transparent

- Rapid display response < 1 ms</li>

- Frame Buffer

- High transparency

- · Reliable, long operating life

- 2-bit interface

# 2 Installation and handling

Do not drop, bend, or flex the display. Do not allow objects to strike the surface of the display.

**CAUTION:** The display uses CMOS and power MOS-FET devices. These components are electrostatic sensitive. Unpack, assemble, and examine this assembly in a static-controlled area only. When shipping, use packing materials designed for protection of electrostatic-sensitive components.

# 2.1 Mounting TFEL display

Properly mounted, TFEL displays can withstand high shock loads as well as severe vibration found in demanding applications. However the glass panel used in a TFEL display will break if subjected to bending stresses, high impact, or excessive loads.

Avoid bending the display. Stresses are often introduced when a display is mounted into a product. Ideally, the mounting tabs of the display should be the only point of contact with the system. Use a spacer or boss for support; failure to do so will bend the display and cause the glass to break. The instrument enclosure or frame should not flex or distort in such a way that during use the bending loads might be transferred to the display. Mounting surfaces should be flat to within  $\pm 0.6$  mm ( $\pm 0.025$ "). Use all the mounting holes provided. Failure to do so will impair the shock and vibration resistance of the final installation.

**WARNING:** These products generate voltages capable of causing personal injury (high voltage up to  $235 \, V_{AC}$ ). Do not touch the display electronics during operation.

## 2.2 Cable length

A maximum cable length of 600 mm (24 in.) is recommended. Longer cables may cause data A maximum cable length of 0.6 m (24 in.) is recommended. Longer cables may cause data transfer problems between the data transmitted and the display input connector. Excessive cable lengths can pick up unwanted EMI. Contact Beneq Products Application Engineering for more information.

#### 2.3 Cleaning

As with any glass, clear plastic or coated surface, care should be taken to minimize scratching. Clean the display with mild, water-based detergents only. Apply the cleaner sparingly to a soft cloth, and then wipe the display. Disposable cleaning cloths are recommended to minimize the risk of inadvertently scratching the display with particles embedded in a re-used cloth. Particular care should be taken when cleaning displays with anti-glare and anti-reflective films.

### 2.4 Avoiding latent image

As with other displays, use a screensaver or image inversion to avoid causing latent image on the display. Displaying fixed patterns on the screen can cause latent image, where luminance variations can be noticed.

# 3 Specifications

Performance characteristics are guaranteed when measured at 25 °C with rated input voltage unless otherwise specified.

#### 3.1 Control basics

The TFEL panel is a matrix structure with column and row electrodes arranged in an X-Y formation. Light is emitted when an AC voltage of sufficient amplitude is applied at a row-column intersection. The display operation is based on the symmetric, line-at-a-time data addressing scheme.

#### 3.2 Power

The supply voltages are shown in Table 1. All internal high voltages are generated from the display supply voltage ( $V_H$ ). The logic supply voltage ( $V_L$ ) should be present whenever video input signals or  $V_H$  is applied. The minimum and maximum specifications in this manual should be met, without exception, to ensure the long-term reliability of the display. Beneq does not recommend operation of the display outside these specifications.

**Table 1. DC input requirements**

| Description                                   | Min   | Nominal /<br>Typical | Max   | Absolute Max |

|-----------------------------------------------|-------|----------------------|-------|--------------|

| Logic supply voltage (V <sub>L</sub> )        | 4.5 V | 5.0 V                | 5.5 V |              |

| Display supply voltage (V <sub>H</sub> )      | 17 V  | 24 V                 | 27 V  |              |

| Logic input current ( $V_L = 5 V$ )           |       |                      |       | 100 mA       |

| Display input current (V <sub>H</sub> = 12 V) |       |                      |       | 1.5 A        |

| Power                                         |       | 17 W                 | 27 W  | 36 W         |

**Table 2. Video input requirements**

| Description                    | Minimum | Maximum |

|--------------------------------|---------|---------|

| Absolute maximum input voltage | -0.3% V | 5.5 V   |

| Logic low input voltage        | 0 V     | 0.8 V   |

| Logic high input voltage       | 2.4 V   | 5 V     |

There is no overcurrent protection on either the  $V_H$  or  $V_L$  inputs to protect against catastrophic faults. Beneq recommends the use of a series fuse on the 24 volt supply  $(V_H)$ . A general guideline is to rate the fuse at 1.8 to 2 times the display maximum current rating.

During the power on sequence  $V_L$  must rise before  $V_H$ , and during the power off sequence  $V_H$  must fall before  $V_L$ .

#### 3.3 Connectors

# 3.3.1 Output connector J2, high voltage

Location: On the controller board

Manufacturer: Hirose part number DF3DZ-8P-2H (21)

Purpose: provides the high voltage waveforms required by the driver module

Table 3. Connector J2 pin assignments

| Pin | Name  | Description                             |

|-----|-------|-----------------------------------------|

| 1   | GND   | Ground return                           |

| 2   | CCOMP | Column voltage waveform                 |

| 3   | NC    | Not connected                           |

| 4   | G1    | Discharge path for negative row voltage |

| 5   | G2    | Discharge path for positive row voltage |

| 6   | +RC   | Positive row charge waveform            |

| 7   | +RC   | Positive row charge waveform            |

| 8   | -RC   | Negative row charge waveform            |

Note: The mating connector on the display module has mirrored pin assignments.

# 3.3.2 Output Connector J4, logic

Location: On the controller board, connector J4

Manufacturer: JST part number SM15B-SRSS-TB

Purpose: Provides the control logic required by the driver module

**Table 4. Connector J4 pin assignments**

| Description      | Pin | Pin | Description        |

|------------------|-----|-----|--------------------|

| GND              | 1   | 2   | 5 V supply         |

| 5 V Supply       | 3   | 4   | 3.3 V supply       |

| No connect       | 5   | 6   | DST, column strobe |

| SCK, column clk  | 7   | 8   | CD3, column data   |

| CD2, column data | 9   | 10  | CD1, column data   |

| CD0, column data | 11  | 12  | RCLK, row clk      |

| RDATA, row data  | 13  | 14  | RSTB, row strobe   |

| GND              | 15  |     |                    |

Note: The mating connector on the display module has mirrored pin assignments.

Date: June 19, 2017

#### 3.3.3 Input connector J1

On the controller board Location:

Manufacturer: JST part number B16B-PHDSS-B

Purpose: Receives video signals and DC power from the host system

Table 5. Connector J1 pin assignments

| Description | Pin | Pin | Description |

|-------------|-----|-----|-------------|

| GND         | 1   | 2   | Vн          |

| GND         | 3   | 4   | Vн          |

| VL          | 5   | 6   | GND         |

| GND         | 7   | 8   | DE          |

| NC          | 9   | 10  | NC          |

| D0          | 11  | 12  | D1          |

| HS          | 13  | 14  | VS          |

| VCLK        | 15  | 16  | GND         |

Note: The mating connector on the display module has mirrored pin assignments.

#### 3.3.4 Input connector J1 descriptions

**Table 6. Connector J1 input descriptions**

| Signal                                                                 | Functional description                                                                                         |                              |                           |  |  |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------|--|--|--|

| V <sub>H</sub>                                                         | Power supply. 24 VDC nominal.                                                                                  |                              |                           |  |  |  |

| VL                                                                     | Power supply. 5 VDC nom                                                                                        | Power supply. 5 VDC nominal. |                           |  |  |  |

| DE Data Enable- when high denotes the presence of valid video data D1. |                                                                                                                |                              | alid video data on D0 and |  |  |  |

|                                                                        | Video Data – when both D0 and D1 are high during the active edge of a valid Vclk, the pixel will be turned on: |                              |                           |  |  |  |

|                                                                        | D0 Logic Level                                                                                                 | D1 Logic Level               | Resulting Pixel State     |  |  |  |

| D0, D1                                                                 | 0                                                                                                              | 0                            | Off                       |  |  |  |

|                                                                        | 0                                                                                                              | 1                            | Off                       |  |  |  |

|                                                                        | 1                                                                                                              | 0                            | Off                       |  |  |  |

|                                                                        | 1                                                                                                              | 1                            | On                        |  |  |  |

| VS                                                                     | Vertical Sync. – The rising edge of VS identifies the start of each frame of                                   |                              |                           |  |  |  |

| V 3                                                                    | data. Internally pulled low                                                                                    | through a 47 k ohm resis     | stor.                     |  |  |  |

**Beneq Products Oy** Olarinluoma 9 FI-02200 Espoo

Date: June 19, 2017

Finland

Tel. +358 9 7599 530 Fax +358 9 7599 5310 lumineq@beneq.com

VAT ID FI25115461 www.beneq.com www.lumineq.com

| Signal | Functional description                                                           |  |  |

|--------|----------------------------------------------------------------------------------|--|--|

|        | Horizontal Sync. – identifies the start of each horizontal line of data (ignored |  |  |

| HS     | by the TFEL controller, which uses DE instead.) Internally pulled low through    |  |  |

|        | a 47k ohm resistor.                                                              |  |  |

| VCLK   | Video Clock – video data is latched on the rising edge of VCLK (or the falling   |  |  |

| VCLK   | edge if switch S2 is set to the invert position.)                                |  |  |

| NC     | No Connection—pin is not connected on the circuit board.                         |  |  |

| GND    | Signal return for power supplies and logic inputs.                               |  |  |

# 3.4 Display video input timing

#### 3.4.1 VCLK polarity selection

A switch, S2, is provided on the ELT256.120.90 controller board. The switch allows the VCLK input to be inverted and must be configured by the installer.

The factory set (default) position of S2 is for no VCLK inversion and should be used with systems that have a VCLK with an active rising edge.

S2 should be moved to the inverted position to accommodate systems with an active falling edge.

#### 3.4.2 Internal frame buffer

This display includes an internal frame buffer. The display frame rate and the display brightness are independent of user-supplied input data timing. The display internal frame frequency is 176 Hz.

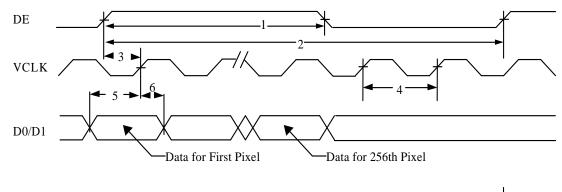

#### 3.4.3 Video timing limits

#### **Table 7. Video Input timing limits**

| #  | Description                | Min. | Max. | Units        |

|----|----------------------------|------|------|--------------|

| 1  | DE high time               | 256  |      | VCLK periods |

| 2  | DE period                  | 26   |      | μs           |

| 3  | DE rise to valid VCLK rise | 15   |      | ns           |

| 4  | VCLK period                | 40   |      | ns           |

| 5  | Data setup to VCLK         | 15   |      | ns           |

| 6  | Data hold from VCLK        | 15   |      | ns           |

| 7  | VS period                  | 122  |      | DE periods   |

| 8  | VS pulse time              | 2    |      | DE periods   |

| 9  | VS non-pulse time          | 120  |      | DE periods   |

| 10 | VS rise to DE rise         | 3    |      | VCLK periods |

#### Notes:

- 1. VCLK is used by for internal logic functions in addition to data clocking and should run continuously for best operation.

- 2. Timing is shown for a VCLK with a rising active edge with switch S2 set to the default position. When switch S2 is set to the inverted position, the timing specifications apply to VCLK after it has been inverted.

- 3. Only the rising edge of VS is important, not the polarity.

- 4. If more than 256 active VCLK edges occur during one DE high time, the excess VCLK edges are ignored.

- 5. If more than 120 DE high times occur during one VS period, the excess DE high times are ignored.

#### **Horizontal Timing**

Figure 1. Video timing signals

# 3.5 Environmental specification

#### 3.5.1 Temperature

Operating:  $0 \text{ to } +40 \text{ }^{\circ}\text{C}$

Non-operating:  $-20 \text{ to } +60 \text{ }^{\circ}\text{C}$

Storage:  $-20 \text{ to } +60 \text{ }^{\circ}\text{C}$

**WARNING:** Certain displayed patterns, such as wide vertical bars and patterns which light approximately 50 % of the pixels per row, can cause high glass temperatures resulting in deformation of the plastic frame, especially when the ambient temperature is high.

**NOTE:** Temperature specifications apply with the display mounted in the plastic frame.

#### 3.5.2 Humidity

Humidity: 0 to 85 % relative humidity, non-condensing.

# 3.6 Electromagnetic Compatibility

The display will not inhibit the end product from complying with FCC Part 15, Subpart J, Class B and EN55022 Class B when housed in a suitable enclosure.

#### **3.7 RoHS**

The display is compliant with European Union 2011/65/EU Directive on the Restriction of Hazardous Substances (RoHS II).

# 3.8 Reliability

MTBF is greater than 50,000 hours with a 90 % confidence level

**WARNING:** excludes latent image which can form over time especially when static patterns are displayed.

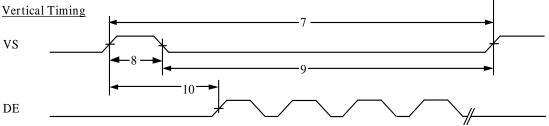

# 3.9 Mechanical Specifications

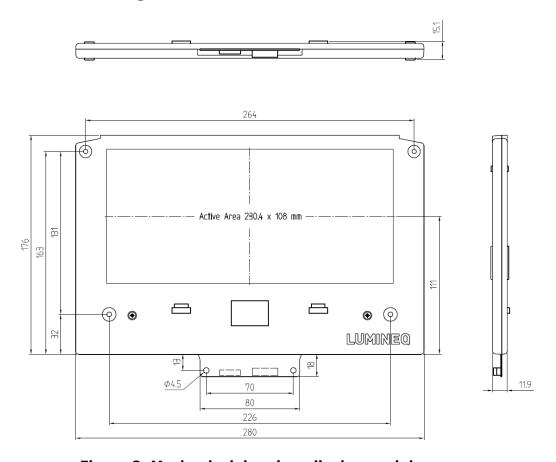

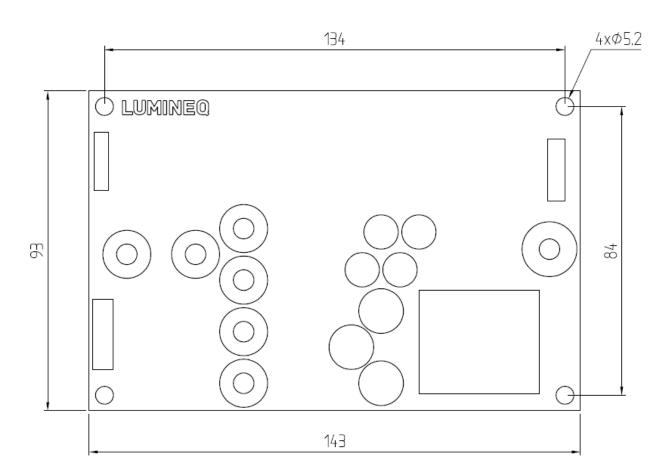

#### 3.9.1 Controller board

Height: 93.0 mm

Width: 143.0 mm

Depth: 28.0 mm maximum

#### 3.9.2 Driver module

Height: 193.4 mm

Width: 280.0 mm

Depth: 12.1 mm

#### 3.9.3 Panel active area

Height: 108.0 mm

Width: 230.4 mm

#### 3.9.4 Pixel pitch

Horizontal: 0.90 mm

Vertical: 0.90 mm

Date: June 19, 2017

#### 3.9.5 Pixel size

Height: 0.80 mm

Width: 0.80 mm

#### 3.9.6 Fill factor

79 % (Fill Factor = 100 % \* emissive area/active area)

#### 3.9.7 Component envelope

Beneq Products reserves the right to relocate components within the constraints of the component envelope without prior customer notification. For this reason, Beneq Products advises users to design enclosure components to be outside the component envelope.

Device designers will need to consider their specific system requirements to determine the spacing necessary to maintain the specified ambient temperature.

Air flow and surrounding component materials will affect the depth of the air gap.

#### 3.9.8 Mechanical drawings

Figure 2. Mechanical drawing, display module

**Beneq Products Oy** Olarinluoma 9 FI-02200 Espoo Finland

Date: June 19, 2017

Tel. +358 9 7599 530 Fax +358 9 7599 5310 lumineq@beneq.com

Figure 3. Mechanical drawing, controller

Tel. +358 9 7599 530 Fax +358 9 7599 5310 lumineq@beneq.com

Document number: ED000830A

www.beneq.com www.lumineq.com

Page | 14

VAT ID FI25115461

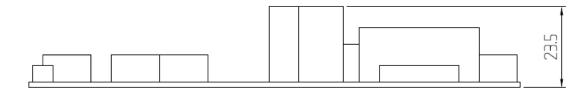

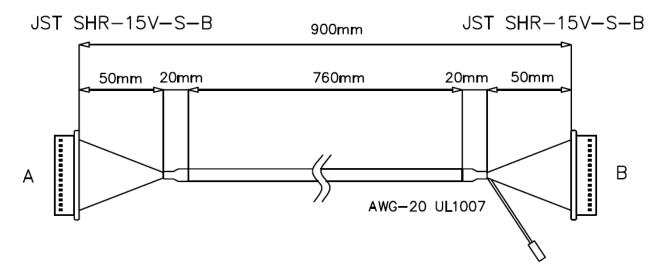

Figure 4. Mechanical drawing, data cable

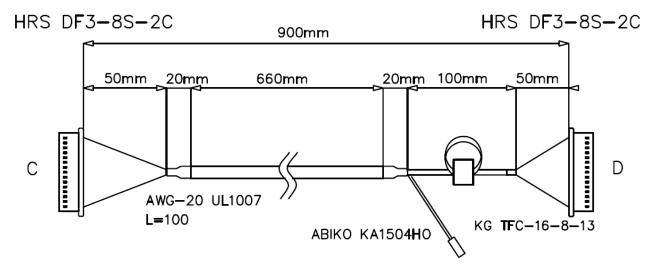

Figure 5. Mechanical drawing, power cable

Date: June 19, 2017

Tel. +358 9 7599 530 Fax +358 9 7599 5310 lumineq@beneq.com

Document number: ED000830A

9 530 VAT ID FI25115461 9 5310 www.beneq.com com www.lumineq.com

## 3.10 Optical specifications

**NOTE:** Luminance specifications are without the plastic frame in the optical path.

#### 3.10.1 "ON" luminance

Center of the active area, all pixels on: Minimum: 60 cd/m<sup>2</sup>, Typical: 80 cd/m<sup>2</sup>

#### 3.10.2 Maximum "OFF" luminance

Maximum off luminance: 0.35 cd/m<sup>2</sup>

#### Notes:

- 1. Measured at 5 points, with all pixels black, maximum luminance setting.

- 2. The five points are defined as the center of the active area plus the four corners.

#### 3.10.3 Luminance non-uniformity

Luminance non-uniformity: 35 %, maximum

The luminance non-uniformity is the maximum difference between any two of five points is defined by the following equation:

LNU = [1 - (lowest luminance)/ (highest luminance)] \* 100.

#### Notes:

- 1. Measured at 5 points, with all pixels yellow

- 2. The five points are defined as the center of the active area plus the four corners

#### 3.10.4 Chromaticity

Approximate color coordinates (x, y): 0.527, 0.468

# 4 Description of warranty

Seller warrants that the Goods will conform to published specifications and be free from defects in material during warranty time from delivery. To the extent that goods incorporate third-party-owned software, seller shall pass on seller's licensor's warranty to buyer subject to the terms and conditions of seller's license.

Warranty repairs shall be warranted for the remainder of the original warranty period. Buyer shall report defect claims in writing to seller immediately upon discovery, and in any event, within the warranty period. Buyer must return goods to seller within 30 days of seller's receipt of a warranty claim notice and only after receiving seller's return goods authorization. Seller shall, at its sole option, repair or replace the goods.

If goods were repaired, altered or modified by persons other than seller, this warranty is void. Conditions resulting from normal wear and tear and buyer's failure to properly store, install, operate, handle or maintain the goods are not within this warranty. Repair or replacement of goods is seller's sole obligation and buyer's exclusive remedy for all claims of defects. If that remedy is adjudicated insufficient, Seller shall refund buyer's paid price for the goods and have no other liability to buyer.

All warranty repairs must be performed at seller's authorized service center using parts approved by seller. Buyer shall pay costs of sending goods to seller on a warranty claim and seller shall pay costs of returning goods to buyer. The turnaround time on repairs will usually be 30 working days or less. Seller accepts no added liability for additional days for repair or replacement.

If seller offers technical support relating to the goods, such support shall neither modify the warranty nor create an obligation of seller. Buyer is not relying on seller's skill or judgment to select goods for buyer's purposes. Seller's software, if included with goods, is sold as is, and this warranty is inapplicable to such software.

SELLER DISCLAIMS ALL OTHER WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

# 5 Ordering information

| Product       | Part number   | Description                                   |  |  |

|---------------|---------------|-----------------------------------------------|--|--|

| ELT256.120.90 | 997-5885-00LF | Transparent TFEL Display with plastic frames. |  |  |

# 6 Support and service

Beneq Products is a Finnish company based in Espoo, Finland, with a world-wide sales distribution network. Full application engineering support and service are available to make the integration of Lumineq displays as simple and quick as possible for our customers.

**RMA Procedure:** For a Returned Material Authorization number, please contact Beneq Products Oy by email (rma.lumineq@beneq.com) with the model number(s), serial number(s) and brief description of the problem. When returning goods for repair, please include a brief description of the problem, and mark the outside of the shipping container with the RMA number.

#### 7 RoHS II

Beneq Products OY is committed to continuous improvement. As part of this process we are fully in support of EU directive 2011/65/EU, the Restriction of Hazardous Substances, commonly known as RoHS II or RoHS Recast, which, compared to RoHS, keeps the restrictions on the original six hazardous substances, including lead (Pb) in electronic equipment. It also expands these restrictions to previously exempted categories including medical devices and monitoring and control instruments.

Beneq part number with an "LF" suffix designation indicates RoHS compliance, as shown on the part number label affixed to the display and on the box containing the display.

This document is compiled and kept up-to-date as conscientiously as possible. Beneq cannot, however, guarantee that the data are free of errors, accurate or complete and, therefore, assumes no liability for loss or damage of any kind incurred directly or indirectly through the use of this document. The information in this document is subject to change without notice. All texts, pictures, graphics and any other contents of this document and their layout are protected by copyright and other protective laws. The aforementioned contents may not be duplicated, modified or used in other electronic or printed publications without the prior consent of Beneq. Unless otherwise stated, all trademarks are protected under trademark laws, especially the Beneq trademarks, logos, emblems and nameplates. The patents and trademarks presented in this document are the intellectual property of Beneq Oy. Beneq, Lumineq and TASEL are registered trademarks of Beneq Oy.

Date: June 19, 2017